# MOS/LSI DATABOOK

# NATIONAL SEMICONDUCTOR

575 E. MIDDLEFIELD RD./MT. VIEW, CALIF. 94040

(415) 961-7000

# SECTION 9 CONTROLLER ORIENTED PROCESSOR SYSTEMS (COPS)

**COPS**

#### National's Controller Oriented Processor Systems

#### introduction

National's Controller Oriented Processor Systems provide a low cost solution to low end computing and control problems. Manufactured by NSC's volume proven P-channel MOS/LSI controller process, the COPS offers an attractive, low risk alternative to custom LSI when available development time is short and cost is critical. Single mask programming of the on-chip control ROM allows delivery of prototype devices directly from the calculator production lines.

Architectural features of the COPS permit rapid efficient design and implementation of systems using key or switch inputs and display or printer outputs. Interface circuits in the COPS are designed to allow expansion of system memory and I/O capability without sacrificing the "lowest component count" features of the set.

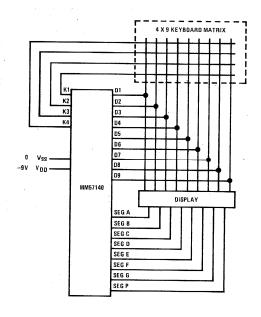

Elements in the COPS family provide four levels of processing capability from the dedicated MM57140 single chip system with direct display and keyboard interface to the highly flexible MM5782 based multichip systems.

#### features

- National's COPS feature P-channel metal gate process for lowest cost

- Single power supply operation

- CMOS compatibility

- Serial I/O ports for easy communication between processor and peripheral circuits

- Expandable RAM and ROM

- BCD in/out option for applications flexibility

- Direct interfacing to keyboard and display

- 10 μs instruction cycle

- 4-bit data/8-bit instruction word

- Single mask programmable

- Learn mode programmability

#### **COPS** elements

- Automobile displays

- Oven controllers

- Vending machines

- Specialty calculators

- Simple electronic cash registers

- Computing instruments

- Electronic scales

- Printer/display controller

- Appliance controller

- Data terminal controller

- Automated gasoline pumps

- Alpha/numeric programmable calculators

#### applications

MM5781 - 16k control and ROM element

MM57129 - 32k control and ROM element

MM5782 — Memory and processor element

MM5785 — Memory interface to 1024 x 1 RAM

MM5785 — Memory interface to 1024 x 1 RAM devices

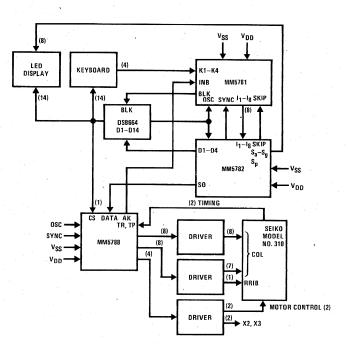

MM5788 — Printer interface to Seiko printers

MM5799 — Single chip microcomputer

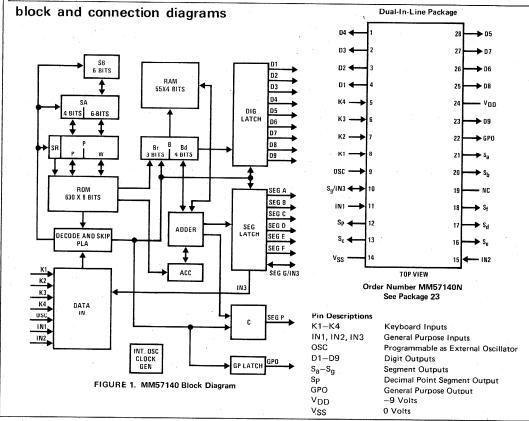

MM57140 – Single chip microcomputer – DS8664/5/6 – Decoder, digit driver and oscillator

DS8692 — Hex power driver (single)

DS8693 — 8-bit latch and driver (source)

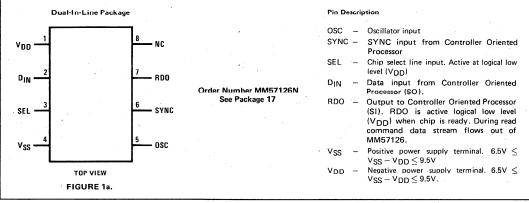

MM57126 — Programmer shift register

9

#### MM5781, MM5782 Controller Oriented Processor Systems

#### general description

The National MM5781, MM5782 is a set of MOS/LSI circuits designed for application in low cost, versatile, dedicated or custom programmed calculator and control systems.

A full capability scientific or business calculator system can be built using only four circuits, plus the keyboard, case, battery and LED display. Application as a printing calculator or in electronic cash registers is possible using National's MM5788 printer interface circuit. Both the basic ROM instruction store and read/write store are expandable.

#### features

- 2048 x 8-bit ROM, expandable to 8192 x 8

- 640 bits (160 digits) RAM, expandable using MM5785

- 8 parallel outputs, coded as 7-segment + d.p. or BCD

- Serial data I/O for easy interface to peripheral circuits

- 3 general purpose I/O latches

- Blanking output

- 4 strobed key inputs

- 10µs micro-instruction cycle time

- Single power supply operation

- 4-bit data/8-bit instruction words

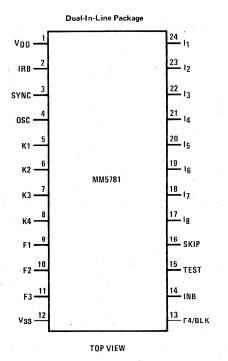

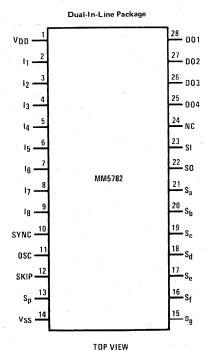

#### connection diagrams

Order Number MM5781N See Package 22

Order Number MM5782N See Package 23

#### absolute maximum ratings

Voltage at Any Pin Relative to VSS (All Other Pins Connected to VSS) Ambient Operating Temperature Ambient Storage Temperature Lead Temperature (Soldering, 10 seconds) V<sub>SS</sub> +0.3V to V<sub>SS</sub> -12V

0°C to +70°C -55°C to +125°C 300°C

#### dc electrical characteristics

$(0^{\circ}C \text{ to } +70^{\circ}C \text{ unless otherwise noted})$

| PARAMETER                                                                 | CONDITIONS                                    | MIN                  | TYP      | MAX                  | UNITS |

|---------------------------------------------------------------------------|-----------------------------------------------|----------------------|----------|----------------------|-------|

| Operating Voltage (VSS - VDD)                                             |                                               | 7.9                  |          | 9.5                  | / V   |

| Operating Supply Current (IDD)                                            | $V_{SS} - V_{DD} = 9.5V, T_{A} = 25^{\circ}C$ | /.0                  |          | 5.5                  | V     |

| MM5781                                                                    | VSS = VDD = 3.3V, 1A = 25 C                   |                      | -7       | -12                  | m A   |

| MM5782                                                                    |                                               |                      | /<br>−15 | -25                  | mA    |

| OSC Input Voltage Levels                                                  |                                               |                      | 13       | 25                   | IIIA  |

| Logical High Level (VIH)                                                  | Vss - Vpp = 7.9V                              | \/ 10                |          |                      |       |

| Logical Low Level (VIL)                                                   | Vss - V <sub>DD</sub> = 9.5V                  | V <sub>SS</sub> -1.0 |          | V <sub>DD</sub> +1.5 | V     |

|                                                                           |                                               |                      |          | VDD+1.5              | V     |

| OSC Input Resistance to V <sub>SS</sub><br>MM5781 Only (R <sub>IN</sub> ) | (Note 3), <i>(Figure 2)</i>                   |                      | 3        | 6                    | kΩ    |

| INB, K1-K4, F1-F3 Input                                                   |                                               |                      |          |                      |       |

| Voltage Levels                                                            |                                               |                      |          |                      |       |

| Logical High Level (VIH)                                                  | V <sub>SS</sub> - V <sub>DD</sub> = 7.9V      | V <sub>SS</sub> -3.2 |          |                      | V     |

|                                                                           | V <sub>SS</sub> - V <sub>DD</sub> = 9.5V      | V <sub>SS</sub> -4.5 |          |                      | ·     |

| Logical Low Level (VIL)                                                   | $7.9V \le V_{SS} - V_{DD} \le 9.5V$           |                      |          | V <sub>DD</sub> +1.5 | V •   |

| INB, K1-K4 Input Current Levels                                           |                                               |                      |          |                      | ,     |

| Logical High Level Current (I <sub>IH</sub> )                             | V <sub>IH</sub> = V <sub>SS</sub> - 3.2V      |                      | 1        | -350                 | μΑ    |

|                                                                           | (LED Display Interface)                       |                      |          |                      |       |

| Logical Low Level Current (IIL)                                           | V <sub>IL</sub> = V <sub>SS</sub> - 32V       | -20                  |          | 1 .                  | μΑ    |

|                                                                           | (Fluorescent Display Interface)               |                      |          |                      |       |

| IRB Input Voltage Levels                                                  |                                               |                      | 4.       |                      |       |

| Logical High Level (VIH)                                                  | 7.9V≤V <sub>SS</sub> −V <sub>DD</sub> ≤9.5V   | V <sub>SS</sub> -3.5 |          |                      | V     |

| Logical Low Level (VIL)                                                   | $V_{SS} - V_{DD} = 7.9V$                      |                      |          | V <sub>DD</sub> +2.5 | · V   |

|                                                                           | $V_{SS} - V_{DD} = 9.5V$                      |                      |          | V <sub>DD</sub> +3.0 | V     |

| I1-I8, SI, SKIP, SYNC and TEST                                            | V <sub>SS</sub> - V <sub>DD</sub> = 7.9V      |                      |          |                      |       |

| Input Voltage Levels                                                      |                                               |                      |          |                      |       |

| Logical High Level (V <sub>IH</sub> )                                     |                                               | V <sub>SS</sub> -1.2 |          |                      | V     |

| Logical Low Level (V <sub>IL</sub> )                                      |                                               | '                    |          | V <sub>SS</sub> -4.0 | V     |

| DO 1, DO 2 and DO 4 Output                                                |                                               |                      |          |                      |       |

| Voltage Levels                                                            |                                               |                      |          |                      |       |

| Logical High Level (V <sub>OH</sub> )                                     | R <sub>L</sub> = 150k, to V <sub>DD</sub>     | V <sub>SS</sub> -1.0 |          | VSS                  | V     |

| Logical Low Level (VOL)                                                   | $I_{OL} = 3\mu A$                             | V <sub>DD</sub>      |          | V <sub>DD</sub> +0.5 | . V   |

| Logical High Level Current (I <sub>OH</sub> )                             | $V_{OH} = V_{DD} + 1.5V$                      |                      |          | 260                  | μΑ    |

|                                                                           | V <sub>SS</sub> -V <sub>DD</sub> = 7.9V       |                      |          |                      |       |

## dc electrical characteristics (con't)

(0°C to +70°C unless otherwise noted)

| PARAMETER                                                               | CONDITIONS                                                       | MIN                  | TYP | MAX                  | UNITS    |

|-------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|-----|----------------------|----------|

| OO 3 Output Voltage Levels                                              |                                                                  |                      |     |                      |          |

| Logical High Level (VOH)                                                | R <sub>L</sub> = 150k, to V <sub>DD</sub>                        | V <sub>SS</sub> -1.0 |     | VSS                  | V        |

| Logical Low Level (VOL)                                                 | $I_{OL} = 3\mu A$                                                | V <sub>DD</sub>      |     | V <sub>DD</sub> +0.5 | V        |

| Logical High Level Current (IOH)                                        | Battery Low "OFF"                                                |                      |     |                      |          |

|                                                                         | $V_{OH} = V_{DD} + 3V$ , $V_{SS} - V_{DD} =$                     | -1.3                 |     | -0.3                 | mA       |

|                                                                         | 9.5V                                                             |                      |     |                      |          |

|                                                                         | $V_{OH} = V_{DD} + 2.5V$ , $V_{SS} - V_{DD} =$                   | -1.0                 |     | -0.4                 | mA       |

|                                                                         | 7.9V                                                             |                      |     |                      | •        |

|                                                                         | Battery Low "ON"                                                 |                      |     |                      |          |

| · · · · · · · · · · · · · · · · · · ·                                   | $V_{OH} = V_{SS} - 3V$ , $V_{SS} - V_{DD} =$                     |                      |     | -0.3                 | mA       |

|                                                                         | 7.9V                                                             |                      |     |                      |          |

|                                                                         | $V_{OH} = V_{SS} - 3V$ , $V_{SS} - V_{DD} =$                     |                      |     | <b>−</b> 0.4         | mA       |

|                                                                         | 9.5V                                                             |                      |     |                      |          |

| S <sub>a</sub> through S <sub>g</sub> and S <sub>p</sub> Output Current | LED Display Interface to DS8867                                  |                      |     |                      |          |

| Levels                                                                  | ,                                                                |                      |     |                      |          |

| Logical High Level Current (IOH)                                        | V <sub>OH</sub> = V <sub>DD</sub> + 5.4V                         |                      |     | -500                 | μΑ       |

| Logical Low Level Current (IOL)                                         | $V_{OL} = V_{DD} + 0.5V$                                         | -1                   |     | 1                    | μΑ       |

| Logical Lott Lotter Latter (*OL)                                        | Fluorescent Display Interface                                    |                      |     |                      |          |

| Logical High Level Current (IOH)                                        | $V_{SS} - V_{DD} = 7.9V, V_{OH} =$                               |                      |     | -300                 | μΑ       |

| 209.027 11.9                                                            | V <sub>SS</sub> – 6V                                             | 1.                   |     |                      |          |

| Logical Low Level Current (IOL)                                         | V <sub>OL</sub> = V <sub>SS</sub> - 32V, R <sub>EXT</sub> = 150k | -20                  |     |                      | μΑ       |

| 203.000                                                                 | to VGG = VSS - 35V                                               |                      |     |                      |          |

| I <sub>1</sub> – I <sub>8</sub> , S0, SYNC and SKIP Output              | Vss – V <sub>DD</sub> = 7.9V                                     |                      | ,   |                      |          |

| Voltage Levels                                                          | VSS - VDD 7.5 V                                                  |                      |     |                      |          |

| Logical High Level (VOH)                                                | ΙΟΗ = -100μΑ                                                     | V <sub>SS</sub> -0.5 |     | V <sub>SS</sub>      | 1        |

| Logical Lingil Level (VOL)                                              | $I_{OL} = 15\mu A$                                               | V <sub>DD</sub>      |     | V <sub>DD</sub> +3.7 | \        |

|                                                                         |                                                                  |                      |     |                      |          |

| F1 — F3 Output Voltage Levels                                           | $7.9V \le V_{SS} - V_{DD} \le 9.5V$                              | V 15                 |     |                      | ,        |

| Logical High Level (VOH)                                                | I <sub>OH</sub> = -30µA                                          | V <sub>SS</sub> -1.5 |     | V <sub>DD</sub> +1.0 | ``       |

| Logical Low Level (VOL)                                                 | I <sub>OL</sub> = 3μA                                            | 1                    | ,   | V DD 11.0            | `        |

| F4 (BLK) Output Voltage Levels                                          | $7.9V \le V_{SS} - V_{DD} \le 9.5V$                              |                      |     |                      |          |

| Logical High Level (VOH)                                                | $I_{OH} = -0.5  \text{mA}$                                       | V <sub>SS</sub> -1.5 |     |                      | \        |

| Logical Low Level (VOL)                                                 | I <sub>OL</sub> = 5μA                                            |                      |     | V <sub>DD</sub> +1.0 | \        |

| Voltage Levels for All Outputs into                                     |                                                                  |                      |     |                      |          |

| CMOS Level                                                              |                                                                  |                      |     |                      |          |

| Logical High Level (VOH)                                                | I <sub>OH</sub> = -10μA                                          | V <sub>SS</sub> -0.5 |     | VSS                  | ٠ ١      |

| Logical Low Level (VOL)                                                 | R <sub>L</sub> = 200k (to V <sub>DD</sub> )                      | VDD                  |     | V <sub>DD</sub> +0.5 | ,        |

| Maximum Allowable Keyboard                                              |                                                                  |                      |     |                      | Jan 10 1 |

| Closed Key Resistance Using INB,                                        |                                                                  |                      |     |                      | 1        |

| F1—F3 or K1—K4 as Inputs                                                |                                                                  |                      |     |                      |          |

| RKEY                                                                    | LED Display Interface                                            |                      |     | 200                  | 2        |

| "NE I                                                                   | Fluorescent Display Interface                                    | I                    |     | 50                   | k k S    |

| PARAMETER                                         | CONDITIONS                                      | MIN  | TYP | MAX  | UNITS    |

|---------------------------------------------------|-------------------------------------------------|------|-----|------|----------|

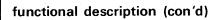

| OSC Input Frequency (1/tp)                        |                                                 | 320  |     | 400  | kHz      |

| OSC Input Duty Cycle                              |                                                 | 46   | 56  | 66   | %        |

| OSC Input Transition Times                        | (Note 3), (Figure 2)                            |      |     |      |          |

| Fall Time (tf)                                    | $C_L = 25 pF$ , $R_L = 6 k\Omega$ , to $V_{SS}$ | 1    |     | 50   | ns       |

| Rise Time (t <sub>r</sub> )                       | RC = 0.15µs                                     |      |     | 350  | ns       |

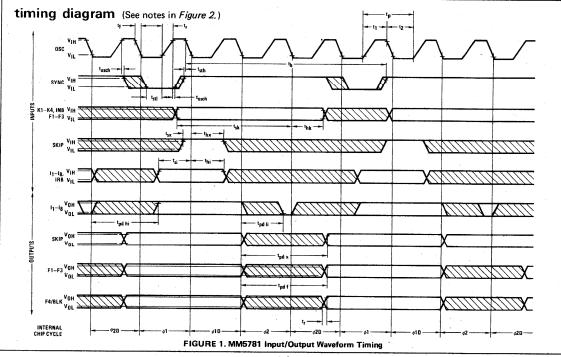

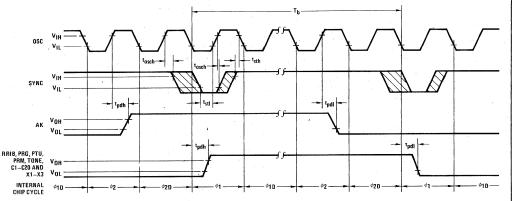

| SYNC Input Timing (Bit Time)                      |                                                 |      |     |      |          |

| Interval Time (tb)                                |                                                 | 10   |     | 12.5 | μs       |

| Hold Time (tosch)                                 |                                                 | 100  |     |      | ns       |

| High-to-Low Set-Up Time (tstl)                    |                                                 | 680  |     |      | ns       |

| Low-to-High Set-Up Time (tsth)                    |                                                 | 100  |     |      | ns       |

| K1 – K4, INB, F1 – F3 Input                       |                                                 |      |     |      |          |

| Timing                                            |                                                 |      |     | 1    |          |

| Set-Up Time (t <sub>sk</sub> )                    | ·                                               | 6.5  |     |      | μs       |

| Hold Time (thk)                                   |                                                 | 1.0  |     |      | μs       |

| SKIP Input Timing                                 |                                                 |      |     |      |          |

| Set-Up Time (t <sub>SX</sub> )                    |                                                 | 280  |     |      | ns       |

| Hold Time (thx)                                   |                                                 | 1.0  |     |      | μs       |

| IRB, I <sub>1</sub> - I <sub>8</sub> Input Timing |                                                 |      |     |      | •        |

| Set-Up Time (tsi)                                 |                                                 | 1.75 |     |      | μς       |

| Hold Time (thi)                                   | i.                                              | 1.0  |     |      | μs       |

| SKIP Output Propagation Delay (tpdx)              | C <sub>LOAD</sub> = 250 pF                      |      |     | 4.4  | μs       |

| I <sub>1</sub> — Ig Output Propagation Delays     | CLOAD = 250 pF                                  |      |     |      | me       |

| Low-to-High (tpdhi)                               | - LOAD - SO P.                                  |      |     | 3.6  | ***      |

| High-to-Low (tpdli)                               |                                                 | l i  | -   | 3.0  | μs<br>μs |

| F1 — F3 Output Propagation Delay                  | C <sub>LOAD</sub> = 100 pF                      | 1    |     | 4.4  |          |

| (t <sub>pdf</sub> )                               | SEOAD 100 bi                                    |      |     | 4.4  | μs       |

| F4 Output Propagation Delay (tpdf)                | CLOAD = 50 pF                                   |      |     | 4.4  |          |

| F4 Output Transition Time                         | - LOAD                                          |      |     | 7.4  | μs       |

| Rise Time (t <sub>r</sub> )                       | C. C. T. > 20 T.                                |      |     |      |          |

| , / LF/                                           | C <sub>LOAD</sub> ≥ 20 pF                       | 0.3  |     | 1    | μs       |

| PARAMETER                                                                                          | CONDITIONS                                                                 | MIN        | TYP | MAX       | UNITS    |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|-----|-----------|----------|

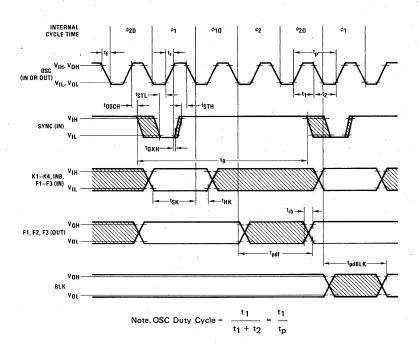

| OSC Input Frequency (1/tp)                                                                         |                                                                            | 320        |     | 400       | k Hz     |

| OSC Duty Cycle                                                                                     |                                                                            | 46         | 56  | 66        | %        |

| OSC Input Transition Times Rise Time (t <sub>r</sub> ) Fall Time (t <sub>f</sub> )                 | RC = $0.15\mu s$<br>CL = $25$ pF, RL = $6$ k $\Omega$ to VSS               |            |     | 350<br>50 | ns<br>ns |

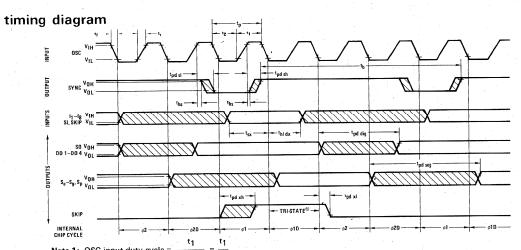

| SYNC Output Cycle (t <sub>b</sub> , Bit Time)                                                      | 320 kHz $\leq$ fOSC $\leq$ 400 kHz                                         | 10         |     | 12.5      | μs       |

| SYNC Output Timing High-to-Low Propagation Delay (tpdsl)                                           | C <sub>L</sub> = 250 pF                                                    | 0.1        |     | 1.65      | μs       |

| Low-to-High Propagation Delay (tpdsh)                                                              |                                                                            | 0.1        |     | 1.25      | με       |

| Initial Transition Delay (t <sub>hs</sub> )                                                        |                                                                            | 0.1        |     | 8.0       | μ        |

| $I_1-I_8$ , SI and SKIP Input Timing<br>Set-Up Time ( $t_{ m SX}$ )<br>Hold Time ( $t_{ m hldx}$ ) |                                                                            | 1.5<br>0.5 |     |           | μ        |

| DO 1 — DO 4 and SO Propagation<br>Delay (t <sub>pddig</sub> )                                      | C <sub>L</sub> = 100 pF (DO 1 - DO 4)<br>C <sub>L</sub> = 250 pF (SO Only) | 0.5        |     | 4         | μ        |

| $S_a-S_g$ , $S_{dp}$ Propagation Delay $(t_{ m pdseg})$                                            | C <sub>L</sub> = 100 pF                                                    |            |     | 6.0       | μ        |

| SKIP Output Timing  tpdxh                                                                          | C <sub>L</sub> = 250 pF                                                    |            |     | 2.4       | μ        |

| tpdxI<br>thx                                                                                       |                                                                            | 0.1        |     | 2.4       | μ        |

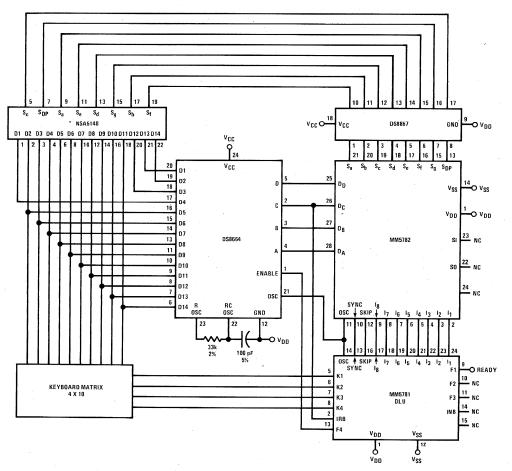

| Interdigit Blanking Time                                                                           | (Figure 5)                                                                 |            |     |           |          |

| T1                                                                                                 | $t_b = 10\mu s$ ,                                                          | 6.5        | 7.5 |           | <i>F</i> |

| Display Blanking                                                                                   | (Figure 5)                                                                 | 38         | 40  |           |          |

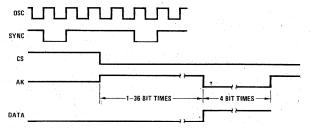

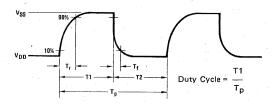

Note 1: USC input duty cycle =  $\frac{t}{t_1 + t_2} = \frac{t}{t_p}$ Note 2: SYNC provides a 1 of 4 timing relationship with OSC input, to establish OSC edges as references for the I/O timing. Note 3: OSC output rise time is determined by capacitive loading and programmable pull-up resistor at the MM5781 input, programmed to provide  $R_C \le 0.15 \mu s$ .

FIGURE 2. MM5782 Input/Output Waveform Timing

#### functional description

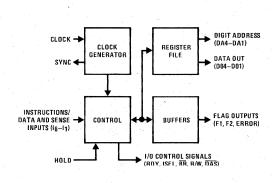

#### MM5781 CONTROL ROM ELEMENT (CRE)

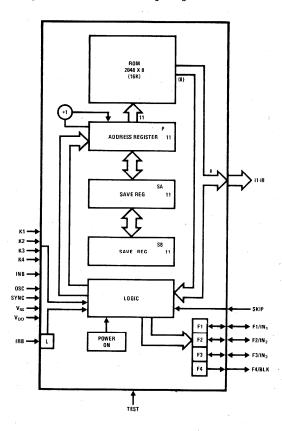

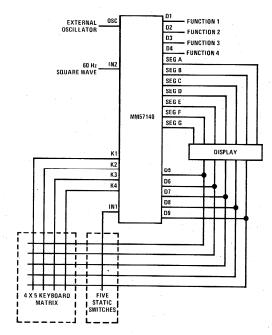

Sixteen kilobits of ROM are organized as 32 pages of 64 8-bit instruction words each. Eight instruction lines and a SKIP signal interconnect the ROM with the MM5782 MPE circuit. Addressing is by an 11-bit P.C. register with two 11-bit push-down address save registers. Four dynamic switch inputs K1–K4 and a static switch input (INB) allow scanning of up to 56 keys and 14 static switches directly. A sixth input (IRB) drives an internal latch that can be used as a program controlled interrupt function.

There are also three program definable I/O ports (F1 - F3) and an additional blanking output F4. The F1-F4 outputs are latched. Four MM5781's may be used with a single MM5782 without additional interface circuits. Figure 3 shows the MM5781 logic diagram.

FIGURE 3. MM5781 Control and ROM Element

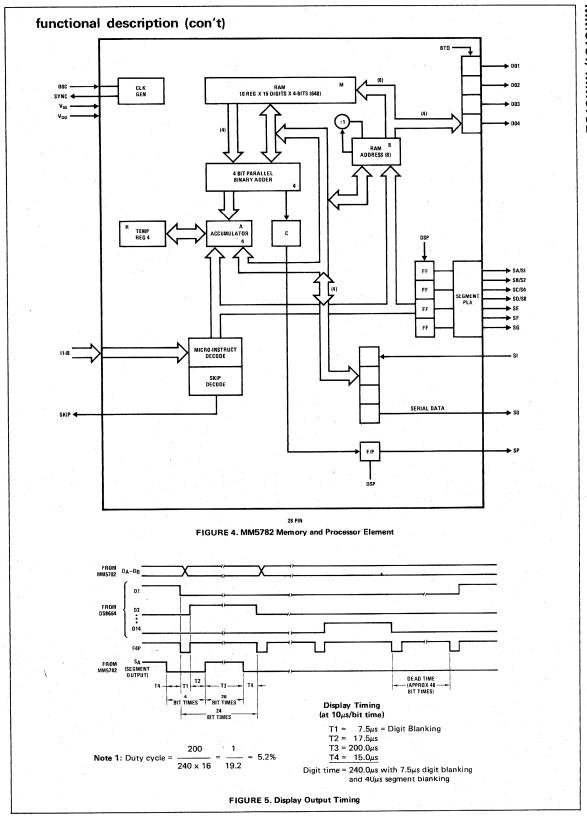

# MM5782 MEMORY AND PROCESSOR ELEMENT (MPE)

The MPE contains 640 bits of RAM organized as 10 16-digit registers. Other register lengths are possible under control of the program. The RAM is addressed by the 8-bit B register. The upper 4 bits (Br) select a particular register and the lower 4 bits (Bd) address the 4-bit words with the register.

Arithmetic and logic functions are performed by the 4-bit binary adder with results stored in the accumulator. The C flip-flop is used for carry bit storage, display decimal point location, and may be utilized to control the skip instruction.

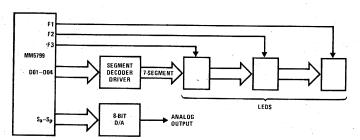

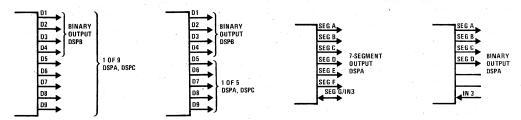

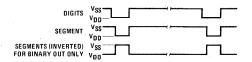

Digit timing information for external keyboard scanning and for driving displays is encoded into a 4-bit code and presented on the DO1–DO4 lines. Eight outputs are decoded by the segment PLA and brought out as 7 segments, BCD, or individually set outputs under program control. Display output timing is shown in Figure 5.

Serial data may be transferred from and into the accumulator A on the Serial Input (SI) and Serial Output (SO) lines. Decimal point position for serial data is given on  $S_p$ .

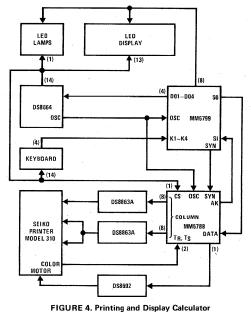

The MM5782 logic diagram is shown in *Figure 4*. Tables I and II list the instruction set and corresponding ROM Codes for the MM5781, MM5782 System.

#### TYPICAL CALCULATION TIMES

System calculation times will vary with the programmed algorithms. The formulas listed reflect one method.

Time to add or subtract two numbers:

$T = ((2N + 20) M + 5N + 10) t_b$

N = number of digits per register

$t_b$  = bit time = 10 $\mu$ s nominal

M = number of shifts required to align decimal point

■ Time to multiply two N-Digit numbers:

$T = ((5N + 15) P + (4N + 20) N + 10) t_b$

P = sum of multiplier digits, i.e., if multiplier = 3211, P = 3 + 2 + 1 + 1 + = 7

Time to divide two N-digit numbers:

$T = ((5N + 15) S + (14N + 40) N + 10) t_b$

S = sum of digits in answer, i.e., if answer = 1234,

S = 1 + 2 + 3 + 4 = 10

Time to enter a BCD number:

$T = 13N t_b$

#### typical applications

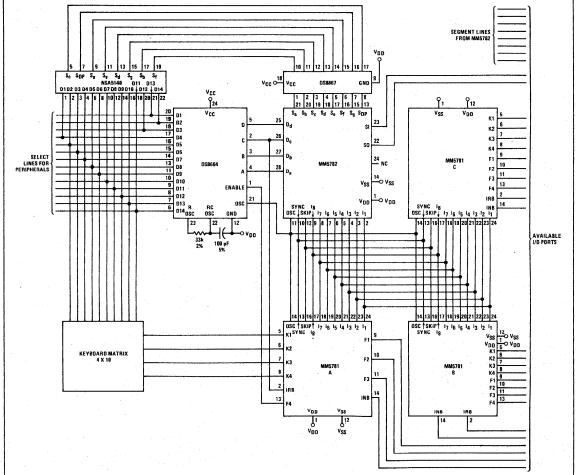

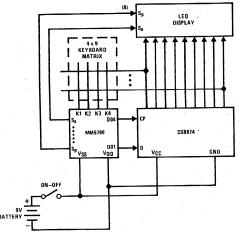

FIGURE 6. Typical 10-Digit Scientific Calculator

Typical application of the MM5781, MM5782 set as a scientific calculator is shown in *Figure 6*. The MM5781 may be programmed to interface with most low cost keyboards which are often the least desirable from a false or multiple entry viewpoint.

When a key closure is sensed by the MM5781, an internal timeout may be programmed to occur. Noise voltages of significant magnitude which occur on the K1-K4 inputs cause the timeout period to be restarted. In this way a key closure is accepted as valid only after a predetermined noise-free period of time. Key release may be validated in the same manner.

#### typical applications (con't)

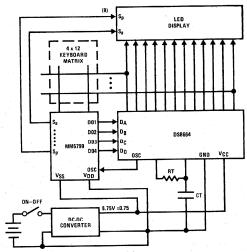

FIGURE 7. Multi-ROM System (Controller, Etc.)

Versatility of the COP set is illustrated in *Figure 7*, showing a multiple ROM system configured for an industrial controller application.

In this application, Control ROM A is programmed to debounce the keyboard inputs as described above.

Control ROMs B and C utilize the K1-K4 lines as general purpose wired inputs. If additional RAM is required, the MM5785 RAM Interface chip allows up to four 1024 x 1 RAMs to be accessed through the SI and SO parts of the MM5782.

# register and I/O port definitions

TABLE I.

|                                            | DESCRIPTIONS                              | DESIGNATIONS                                                           |

|--------------------------------------------|-------------------------------------------|------------------------------------------------------------------------|

| MPE – MEMOI                                | RY AND PROCESSOR ELEMENT                  |                                                                        |

| 640-Bit RAM                                |                                           | M                                                                      |

| 10 Registers x 1                           | 16 Digits x 4 Bits (r x d x z)            |                                                                        |

| 8-Bit RAM Add                              | dress Register                            | В                                                                      |

| B <sub>r</sub> (Registe                    | er) B <sub>d</sub> (Digit)                |                                                                        |

| 4-Bit Accumula                             | ntor                                      | Α                                                                      |

| 4-Bit Holding F                            | Register                                  | н                                                                      |

| 1-Bit Carry Reg                            | jister                                    | С                                                                      |

| 1 Latched Outp                             | out (Decimal Point)                       | Sp                                                                     |

| 4 Latched Digit                            | t Outputs                                 | DO4-DO1                                                                |

| 4 Latched Segn<br>Direct or Deco           | nent Outputs:<br>ded to 7-Segment Outputs | S <sub>a</sub> –S <sub>g</sub>                                         |

| Serial Input and                           | l Output                                  | SI-SO                                                                  |

| CRE CONTR                                  | OL AND ROM ELEMENT                        |                                                                        |

| 16,384-Bit RO                              | vi .                                      | 18-11                                                                  |

| 11-Bit Program                             | Address Register                          | P                                                                      |

| Page P <sub>p</sub><br>Word P <sub>w</sub> | (P11 – P7)<br>(P6 – P1)                   |                                                                        |

| 2 x 11-Bit Prog                            | ram Address Save Registers                | S <sub>A1</sub> -S <sub>A11</sub><br>S <sub>B1</sub> -S <sub>B11</sub> |

| 4 General Purpo                            | ose Flags (Latched)                       | F1-F4                                                                  |

| 4 Keyboard Inp                             | outs                                      | K1-K4                                                                  |

| Static Switch In                           | nput                                      | INB                                                                    |

| Interrupt Input                            |                                           | IRB                                                                    |

#### standard instructions

| <del></del>               | MNEMONIC  | DATA FLOW                                                                               | STATUS - SKIP IF                                       | DESCRIPTION                                                                               |

|---------------------------|-----------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                           | EXC (r)   | $A \leftrightarrow M (B)$<br>$B_r \oplus r \rightarrow B_r$                             |                                                        | Exchange data word at M(B) with A  EXCLUSIVE-OR B <sub>r</sub> with r. r = 0, 1, 2, 3     |

| erations                  | EXC —(r)  | $A \leftrightarrow M (B)$<br>$B_r \oplus r \rightarrow B_r, B_d - 1 \rightarrow B_d$    | B <sub>d</sub> → 15                                    | Exchange and decrement B <sub>d</sub> EXCLUSIVE OR B <sub>r</sub> with r                  |

| Memory Digit Operations   | EXC +(r)  | $A \leftrightarrow M$ (B)<br>$B_r \oplus r \rightarrow B_r$ , $B_d + 1 \rightarrow B_d$ | $B_d \rightarrow 0 \text{ or}$<br>$B_d \rightarrow 13$ | Exchange and increment B <sub>d</sub> EXCLUSIVE OR B <sub>r</sub> with r                  |

| emory [                   | MTA (r)   | $M (B) \rightarrow A$ $B_r \oplus r \rightarrow B_r$                                    |                                                        | Load accumulator with data word at M (B)  EXCLUSIVE OR B <sub>r</sub> with r              |

|                           | LM (Y)    | $Y \rightarrow M (B)$<br>$B_d + 1 \rightarrow B_d$                                      |                                                        | Load memory with Y, Y = 0, 1, 2, 15<br>Increment B <sub>d</sub>                           |

| Memory Bit<br>Operations  | SM (Z)    | 1 → M (B, Z)                                                                            |                                                        | Set bit Z of M (B), Z = 1, 2, 4, 8                                                        |

| nory                      | RSM (Z)   | $0 \rightarrow M (B, Z)$                                                                |                                                        | Reset bit Z of M (B)                                                                      |

| Op Mer                    | TM (Z)    |                                                                                         | M (B, Z) = 0                                           | Test bit Z of M (B), skip if zero                                                         |

| ions                      | LB (r, d) | $r \rightarrow B_r$ , $d \rightarrow B_d$                                               |                                                        | r = 0, 1, 2, 3, d = 0, 11, 12, 13, 14, 15<br>Load B register. Successive LB's are ignored |

| Operat                    | LBL (I)   | $18_{-5} \rightarrow B_r, 1_{4-1} \rightarrow B_d$                                      |                                                        | 2 microcycle instruction. Load next ROM word into B register                              |

| Address                   | АТВ       | $A \rightarrow B_d$                                                                     |                                                        | Transfer contents of accumulator to B <sub>d</sub> register                               |

| Memory Address Operations | вта       | $B_d \rightarrow A$                                                                     |                                                        | Transfer contents of 8 <sub>d</sub> register to                                           |

| _                         | HXBR      | H ↔ B <sub>r</sub>                                                                      |                                                        | Exchange contents of H and B <sub>r</sub> registers                                       |

| T                                     | MNEMONIC | DATA FLOW                                                         | STATUS - SKIP IF   | DESCRIPTION                                                           |

|---------------------------------------|----------|-------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|

|                                       | GO TO    | I <sub>6</sub> - I <sub>1</sub> → P <sub>W</sub>                  |                    | Load next ROM instruction address. If on                              |

|                                       | (GO)     | If Pp = 1111X:11110 → Pp                                          |                    | page 368 or 378 reset page address to 368                             |

| Ì                                     | CALL     | 16 - I <sub>1</sub> → P <sub>W</sub> , IIIII → P <sub>P</sub>     |                    | Call subroutine. If not page 36g or 37g, set                          |

|                                       |          | If Pp ≠ IIIIX: SA → SB,                                           |                    | page address to 378. Push down address                                |

|                                       |          | P + 1 → S <sub>A</sub>                                            |                    | save registers                                                        |

| -                                     | RET      | S <sub>A</sub> → P                                                |                    | Pop up ROM address save registers                                     |

| 1                                     |          | $S_B \rightarrow S_A$ , $S_B \rightarrow S_B$                     |                    |                                                                       |

| . 1                                   | RETS     | S <sub>A</sub> → P                                                |                    | RET, then skip next instruction upon return                           |

| . [                                   |          | $S_B \rightarrow S_A, S_B \rightarrow S_B$                        | SKIP               |                                                                       |

| 1                                     | LG/GO    | Load P                                                            |                    | 2 microcycle operation, long GO TO, load                              |

|                                       |          |                                                                   | ,                  | Pp and P <sub>W</sub>                                                 |

| Sio                                   | LG/CALL  | $S_A \rightarrow S_B$ , $P + 1 \rightarrow S_A$                   |                    | 2 microcycle operation. Long call. Load Pp                            |

| Control Functions                     | 1        | Load P                                                            |                    | and P <sub>W</sub> . Push down address save registers                 |

| Ē.,                                   | CALX (N) | In active CRE                                                     |                    | 2 microcycle operation, N = 1, 2, 3. Call                             |

| ž                                     |          | P + 1 → SA                                                        |                    | additional CRE (N). Push down address save                            |

| ಕಿ                                    | İ        | SA → SB                                                           |                    | registers of active CRE. Load P of selected                           |

|                                       |          | 0 → P                                                             |                    | CRE (N) from next instruction word                                    |

|                                       |          | In selected CRE -                                                 |                    |                                                                       |

|                                       |          | $16 \rightarrow 11 \rightarrow PW$<br>$0 \rightarrow PP$          |                    |                                                                       |

|                                       |          |                                                                   |                    | 2 microcycle operation. Return to CRE (O).                            |

|                                       | RTX (0)  | In active CRE —                                                   |                    | Pop up ROM address save registers in CRE (O).                         |

|                                       |          | $P + 1 \rightarrow S_A, S_A \rightarrow S_B$<br>$0 \rightarrow P$ |                    | Push down ROM address save registers of active                        |

|                                       |          | In CRE (O) -                                                      |                    | CRE                                                                   |

|                                       |          | S <sub>A</sub> → P                                                |                    |                                                                       |

|                                       |          | S <sub>B</sub> → S <sub>A</sub>                                   | · _                |                                                                       |

|                                       | NOP      |                                                                   | 1                  | No operation                                                          |

|                                       | AD       | M + A → A                                                         |                    | Add M (B) to A, store sum in A                                        |

|                                       |          | C + M + A → A                                                     |                    | Add carry bit to M (B), add sum to A,                                 |

|                                       | ADD:     | $0 \rightarrow C \text{ if } A < 10$                              | -                  | store sum in A                                                        |

|                                       |          | 1 → C if A ≥ 10                                                   | A < 10             | Set C if $A \ge 10$ , reset C if $A < 10$                             |

|                                       |          |                                                                   |                    | Subtract A from M                                                     |

|                                       | SUB      | $M + \overline{A} + C \rightarrow A$                              |                    |                                                                       |

|                                       |          | Overflow → C                                                      | Overflow           | Overflow to C                                                         |

| raţi                                  | COMP     | Ā→A                                                               |                    | One's complement of A to A                                            |

| Arithmetic Operations                 | 0TA      | 0 → A                                                             |                    | Clear accumulator                                                     |

| Ę.                                    | ADX (Y)  | $A + Y \rightarrow A$                                             | No overflow, Y ≠ 6 | Add constant (Y) to A, store sum in A                                 |

| Ĕ.                                    |          |                                                                   |                    | Y = 1, 2, 15                                                          |

| Ā                                     | HXA      | H↔A                                                               |                    | Exchange contents of H register with A                                |

|                                       | TAM      | İ                                                                 | A = M (B)          | Compare contents of A to M (B), skip if                               |

|                                       |          |                                                                   |                    | A = M (B)                                                             |

|                                       | sc       | 1 → C                                                             |                    | Set C register                                                        |

| N .                                   | RSC      | 0 → C                                                             |                    | Reset C register                                                      |

|                                       | · ·      | 1                                                                 | C = 0              | Skip if C = 0                                                         |

| · · · · · · · · · · · · · · · · · · · | TC       | P                                                                 | U=0                |                                                                       |

|                                       | втр      | B <sub>d</sub> → DO1 — DO1                                        | 14                 | Transfer contents of B <sub>d</sub> to digit output latches           |

|                                       | DSPA     | $A \rightarrow S_a - S_d$                                         |                    | A4-A1 to output latches, directly to outputs Sa-Sd                    |

|                                       |          | $0 \rightarrow S_e - S_g$                                         |                    | 0 to outputs S <sub>e</sub> —S <sub>g</sub> C to S <sub>p</sub> latch |

| part                                  |          | $C \rightarrow S_p$                                               |                    | A to output latches, 7-segment decoded to Sa-Sg                       |

| )<br>Out                              | DSPS     | $A \rightarrow S_a - S_g$                                         |                    | C to So latch                                                         |

| Input/Output                          | 1        | C → S <sub>p</sub>                                                |                    | Exchange accumulator with serial input/output                         |

| 5                                     | AXO      | SI → A                                                            |                    | exchange accumulator with serial imput/output                         |

|                                       | 1        | A → SO                                                            |                    | N = 1, 2, 3, 4. Load F (N) from next instruction word                 |

|                                       | LDF      | I → F (N)                                                         |                    | 2 microcycle instruction                                              |

|                                       |          |                                                                   | +                  |                                                                       |

| 1.4 s 5 1                             | TIN      | The second of the second                                          | INB = 1            | Test INB. Active state of input is programmable                       |

| est                                   | TK (N)   | if F4 = 0                                                         | K (N) = 1          | N = 1, 2, 3, 4. Active state of input is programmable                 |

|                                       | 1        | if F4 = 1                                                         | F (N) = 1          | N = 1, 2, 3                                                           |

| =                                     | 1        |                                                                   |                    |                                                                       |

| Input Test                            | ТКВ      |                                                                   | K (N) = 1          | N = 1, 2, 3, 4. Skip if any K input active                            |

# operation codes

TABLE II.

|                               | OF    | CODE                          |       |                  | MNEM                       | ONIC              |                          |

|-------------------------------|-------|-------------------------------|-------|------------------|----------------------------|-------------------|--------------------------|

| l <sub>8</sub> l <sub>7</sub> | 16 15 | l <sub>4</sub> l <sub>3</sub> | 12 11 | 00               | 01                         | 10                | 11                       |

| 00                            | XX    | 00                            | - 00  | NOP.             | DSPA                       | COMP              | OTA                      |

| 00                            | XX    | 00                            | 01    | HXB <sub>r</sub> | DSPS                       | AXO               | HXA                      |

| 00                            | XX    | 00                            | 10    | ADD -            | AD                         | SUB               | TAM                      |

| 00                            | XX    | 00                            | 11    | sc               | LBL                        | RSC               | LDF                      |

| 00                            | ××    | 01                            | 00    | TK1              | TK2                        | ткз               | TK4                      |

| 00                            | XX    | 01                            | - 01  | TIR              | TKB                        | BTD               | TIN                      |

| 00                            | XX    | 01                            | 10    | MTA (r)          |                            |                   |                          |

| 00                            | XX    | 01                            | 11    | EXC (r)          |                            |                   |                          |

| 00                            | XX    | 10                            | 00    | EXC- (r)         |                            |                   |                          |

| 00                            | XX    | 10                            | 01    | EXC+ (r)         |                            |                   |                          |

| 00                            | XX    | 10                            | 10    | LB (r, 0)        |                            |                   |                          |

| 00                            | XX    | 10                            | 11    | LB (r, 11)       |                            |                   |                          |

| 00                            | xx    | 11                            | 00    | LB (r, 12)       |                            |                   |                          |

| 00                            | XX    | 11                            | 01    | LB (r, 13)       |                            |                   |                          |

| 00                            | XX    | . 11                          | 10    | LB (r, 14)       |                            |                   |                          |

| 00                            | XX    | 11                            | 11    | LB (r, 15)       |                            |                   |                          |

| 01                            | 00    | 00                            | xx    | RET              | RETS                       | RSM (8)           | вта                      |

| 01                            | 00    | 01                            | xx    | TM (1)           | TM (2)                     | TM (4)            | TM (8)                   |

| 01.                           | 00    | 10                            | xx    | RSM (1)          | SM (1)                     | SM (8)            | RSM (4)                  |

| 01                            | 00    | . 11                          | XX    | RSM (2)          | TC                         | SM (2)            | SM (4)                   |

| 01                            | 01    | 00                            | xx    | АТВ              | ADX (1)                    | ADX (2)           | ADX (3)                  |

| .01                           | -01   | 01                            | xx    | ADX (4)          | ADX (5)                    | ADX (6)           | ADX (3)                  |

| 01                            | 01    | 10                            | xx    | ADX (8)          | ADX (9)                    | ADX (10)          | ADX (7)                  |

| 01                            | 01    | . 11                          | XX    | ADX (12)         | ADX (13)                   | ADX (14)          | ADX (11)                 |

| 01                            | 10    | 00                            | ×x    | , CALX           | LG (35, 34)                | LG (33, 32)       | LG (31, 30               |

| 01                            | 10    | 01                            | xx    | LG (27, 26)      | LG (25, 24)                | LG (33, 32)       | LG (31, 30<br>LG (21, 20 |

| 01                            | 10    | 10                            | XX    | LG (17, 16)      | LG (25, 24)<br>LG (15, 14) | LG (23, 22)       | LG (21, 20<br>LG (11, 10 |

| 01                            | 10    | 11                            | xx    | LG (7, 6)        | LG (5, 4)                  | LG (13, 12)       | LG (11, 10               |

| 01                            | 11    | 00                            | xx    | LM (0)           | LM (1)                     | LM (2)            |                          |

| 01                            | 11    | 01                            | ××    | LM (4)           | LM (5)                     |                   | LM (3)                   |

| 01                            | 11    | 10                            | XX    | LM (8)           | LM (9)                     | LM (6)<br>LM (10) | LM (7)                   |

| 01                            | 11    | 11                            | XX .  | LM (12)          | LM (13)                    | LM (14)           | LM (11)                  |

| 10                            | xx    | xx                            | xx    | CALL             | (10)                       | EM (14)           | LM (15)                  |

| 11                            | XX    | XX ·                          | ××    | GO               |                            |                   |                          |

#### MM5785 RAM interface chip

#### general description

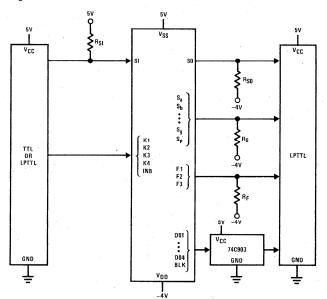

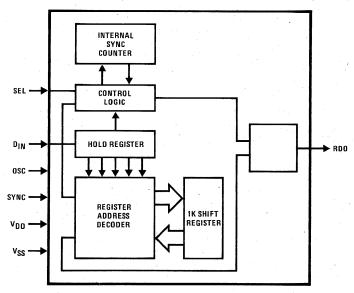

The MM5785 provides the required level conversion between the MM5782 or MM5799 Controller Oriented Processors and external RAM memory. It is intended for use with the MM74C930 and MM2102 1k RAMs as a means of expanding system data storage capability.

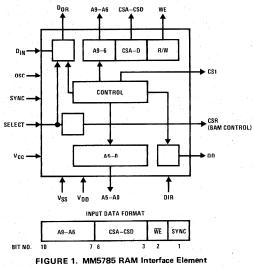

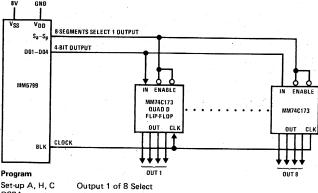

The MM5785 RAM Interface Element allows direct connection of four 1024 x 1 organized read/write memories to the processor. *Figure 1* is a block diagram of the element. Additional interface elements may be added using decoded digit lines from the decoder/driver as chip selects.

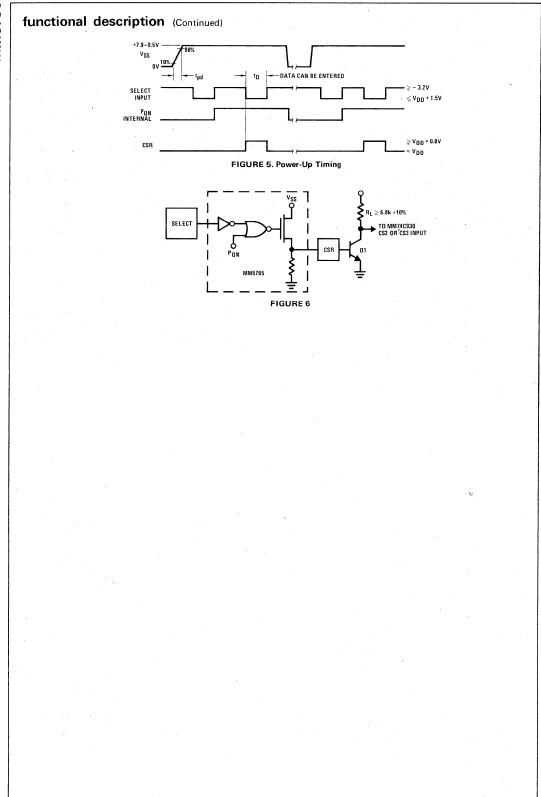

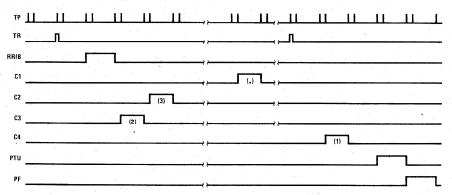

The chip contains a 9-stage address and control bit holding register, a 6-bit incrementing register, control logic and data buffers. A power-on sequence resets all registers when power is applied. (Figure 5.)

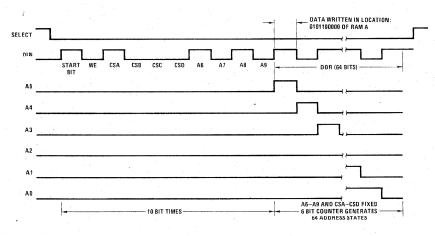

In operation, the chip select is energized and a synchronizing bit followed by the R/W mode select bit, four chip select bits (CSA-CSD), and the register select address bits (A9-A6) are shifted into the holding register (R) through the DIN input port. The 6-bit address register then sequentially addresses each of the 64 bits

within the selected register. In the Write mode, data to be stored is transferred from the processor on the D $_{\mbox{\scriptsize IN}}$  line and outputted to the memory on the DOR line. When reading, data flow is from the memory chip to the DIR pin. The data is buffered and shifted out to the processor on the DO line. All registers are cleared when the address sequence is complete.

Four to sixteen line decoding of the CSA—CSD lines allows addressing of as many as sixteen 1024-bit RAMs using a single MM5785. When interfacing memory circuits such as the MM74C930 or MM2102 to the MM5785, one transistor is required for the CSR (BAM control) line as shown in Figure 2.

#### features

- Directly interfaces the MM5782 and MM5799 Controller Oriented Processors to external RAM

- Compatible with low power CMOS MM74C130 or low cost MM2102 RAM

- Internal power-on clear

## block and connection diagrams

#### Dual-In-Line Package

Order Number MM5785N See Package 23

#### absolute maximum ratings

operating voltage range

Voltage at Any Pin Relative to VSS VSS + 0.3V to VSS - 12V (All Other Pins Connected to VSS)

Ambient Operating Temperature  $0^{\circ}C$  to  $+70^{\circ}C$ Ambient Storage Temperature  $-55^{\circ}C$  to  $+150^{\circ}C$ Lead Temperature (Soldering, 10 seconds)  $300^{\circ}C$

$7.9V \le V_{SS} - V_{DD} \le 9.5V, 4.5V \le V_{CC} - V_{DD} \le 5.5V$  (VSS is always the most positive supply voltage)

# dc electrical characteristics (TA = 25°C)

|                 | PARAMETER                 | CONDITIONS                                                                | MIN                  | TYP | MAX                   | UNITS   |

|-----------------|---------------------------|---------------------------------------------------------------------------|----------------------|-----|-----------------------|---------|

| lpp             | Operating Supply Current  | V <sub>DD</sub> = V <sub>SS</sub> - 9.5V                                  |                      | 8   | 15                    | mA      |

| Icc             | Operating Supply Current  | Capacitive Loading Only                                                   |                      |     | 100                   | μΑ      |

| Icc             | Peak Current              | C <sub>L</sub> = Max, R <sub>L</sub> = Open Circuit,<br>Duration = 400 ns | 1.                   |     | 33                    | mA      |

|                 | OSC Input Levels          |                                                                           |                      |     |                       |         |

| $V_{IH}$        | Logical High Level        | V <sub>DD</sub> = V <sub>SS</sub> - 7.9V                                  | V <sub>SS</sub> -1.0 |     |                       | · v     |

| VIL             | Logical Low Level         | V <sub>DD</sub> = V <sub>SS</sub> - 9.5V                                  |                      |     | V <sub>DD</sub> +1.5  | V       |

|                 | DIN, SYNC Input Levels    |                                                                           |                      |     | 1 .                   |         |

| $v_{iH}$        | Logical High Level        | $V_{DD} = V_{SS} - 7.9V$                                                  | V <sub>SS</sub> -1.2 |     |                       | V       |

| $V_{IL}$        | Logical Low Level         | $V_{DD} = V_{SS} - 9.5V$                                                  |                      |     | V <sub>SS</sub> -4.0  | V       |

|                 | DIR Input Levels          |                                                                           |                      |     |                       |         |

| $v_{IH}$        | Logical High Level        |                                                                           | V <sub>DD</sub> +2.0 |     |                       | V       |

| VIL             | Logical Low Level         |                                                                           |                      |     | V <sub>DD</sub> +0.4  | V.      |

|                 | Select Input Levels       |                                                                           |                      |     |                       |         |

| $V_{IH}$        | Logical High Level        | $V_{DD} = V_{SS} - 7.9V$                                                  | V <sub>SS</sub> -3.2 |     |                       | V       |

| $V_{IL}$        | Logical Low Level         | V <sub>DD</sub> = V <sub>SS</sub> - 9.5V                                  | V <sub>SS</sub> -4.5 |     | V <sub>DD</sub> +1.5  | · V     |

|                 |                           | 7                                                                         |                      |     | V <sub>DD</sub> +1.5  | V       |

| ΉΗ              | Input Current Level       | V <sub>IH</sub> = V <sub>SS</sub> - 3.2V                                  |                      |     |                       |         |

|                 |                           | V <sub>DD</sub> = V <sub>SS</sub> - 7.9V                                  | -350                 |     |                       | $\mu$ A |

|                 | CSR Output Levels         |                                                                           |                      |     |                       |         |

| $V_{\text{OH}}$ | Logical High Level        | I <sub>OH</sub> ≤−100 μA                                                  | V <sub>DD</sub> +0.8 |     |                       | V       |

| VOL             | Logical Low Level         | I <sub>OL</sub> ≤ 10 μA                                                   |                      |     | V <sub>DD</sub> +0.25 | V       |

|                 | DOR, WE, CS 1, A0-A9      |                                                                           |                      |     | . 1                   |         |

|                 | and CSA—CSD Output Levels |                                                                           |                      |     |                       |         |

| νон             | Logical High Level        | IOH ≤ −250 μA                                                             | V <sub>CC</sub> -1.0 |     |                       | V       |

| VOL             | Logical Low Level         | I <sub>OL</sub> ≥ 10 μA                                                   |                      |     | V <sub>DD</sub> +0.5  | V       |

|                 | DO Output Levels          |                                                                           | i i                  |     |                       |         |

| $v_{OH}$        | Logical High Level        | $V_{DD} = V_{SS} - 7.9V$                                                  |                      |     |                       |         |

|                 |                           | I <sub>OH</sub> ≤−100 μA                                                  | V <sub>SS</sub> -0.5 |     |                       | V       |

| $V_{OL}$        | Logical Low Level         | $V_{DD} = V_{SS} - 7.9V$                                                  |                      |     |                       |         |

|                 |                           | $I_{OL} \ge 25 \mu A$                                                     |                      |     | V <sub>DD</sub> +3.7  | V       |

#### ac electrical characteristics

|                   | PARAMETER                    | CONDITIONS                          | MIN  | TYP  | MAX  | UNITS |

|-------------------|------------------------------|-------------------------------------|------|------|------|-------|

|                   | OSC Input Frequency (1/tp)   |                                     | 320  |      | 400  | kHz   |

| ,                 | OSC Duty Cycle               | (Figure 3)                          | 46   | 56   | 66   | %     |

|                   | OSC Input Transition Times   |                                     |      |      |      |       |

| tr                | Rise Time                    | RC = 0.15 μs                        |      |      | 350  | ns    |

| tf                | Fall Time                    | $C_L = 25  pF$ , $R_L = 6  k\Omega$ |      |      | 50   | ns    |

|                   | SYNC Input Timing            | (Figure 3)                          |      |      |      |       |

| tB                | Interval/Bit Time            |                                     | 10.0 |      | 12.5 | , μs  |

| tosch             | Hold Time                    |                                     | 100  |      |      | ns    |

| tstL              | High-to-Low Set-Up Time      |                                     | 680  |      |      | ns    |

| t <sub>stH</sub>  | Low-to-High Set-Up Time      |                                     | 100  |      |      | ns    |

|                   | DIN Input Timing             |                                     |      |      |      |       |

| t <sub>stn</sub>  | Set-Up Time                  |                                     | 2.5  |      |      | μs    |

| thn               | Hold Time                    |                                     | 1.0  |      |      | μs    |

|                   | DIR Input Timing             | C <sub>L</sub> ≤ 50 pF              |      |      |      |       |

| t <sub>str</sub>  | Set-Up Time                  |                                     | 2.5  |      |      | μs    |

| thr               | Hold Time                    |                                     | 1.0  |      |      | μs    |

|                   | SELECT Input Timing          | C <sub>LOAD</sub> ≤ 100 pF,         |      |      |      |       |

|                   | The SELECT Input is normally | (Figure 4)                          |      |      |      |       |

|                   | 75 bits wide and envelopes   |                                     |      |      |      |       |

|                   | the DIN input. The DOR out-  |                                     |      |      |      |       |

|                   | put is the logical-OR of     |                                     |      | <br> |      |       |

|                   | SELECT and DIN               |                                     |      |      |      |       |

|                   | DOR, A0-A9 Output Propaga-   | C <sub>LOAD</sub> = 250 pF          | v    |      |      |       |

|                   | tion Delays                  |                                     |      |      |      |       |

| tpdL,             |                              | ٠.                                  |      |      | 5.0  | μs    |

| tpdH              |                              |                                     |      |      |      |       |

|                   | CSA—CSD Output Propaga-      | C <sub>LOAD</sub> = 100 pF          |      |      |      |       |

|                   | tion Delays                  |                                     |      |      | _    |       |

| <sup>t</sup> pdL  |                              |                                     |      |      | 5.0  | μs    |

| <sup>t</sup> pdH  |                              |                                     |      |      | 10.0 | μs    |

|                   | WE and CS 1 Output Propaga-  | C <sub>LOAD</sub> = 250 pF          |      | -    |      |       |

|                   | tion Delays                  |                                     |      |      | 0.5  |       |

| <sup>t</sup> pdL, |                              |                                     | ,    |      | 2.5  | μs    |

| <sup>t</sup> pdH  | 3                            |                                     |      |      |      | 1     |

|                   | DO Output Propagation Delays | C <sub>LOAD</sub> = 100 pF          |      |      |      |       |

| tpdL.             |                              |                                     |      |      | 2.5  | μs    |

| tpdH              |                              |                                     |      |      |      |       |

|                   | VSS Power "ON" Time          |                                     |      | 4.7  |      |       |

| $t_{po}$          |                              | (Figure 5)                          |      |      | 1.0  | ms    |

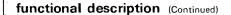

#### functional description

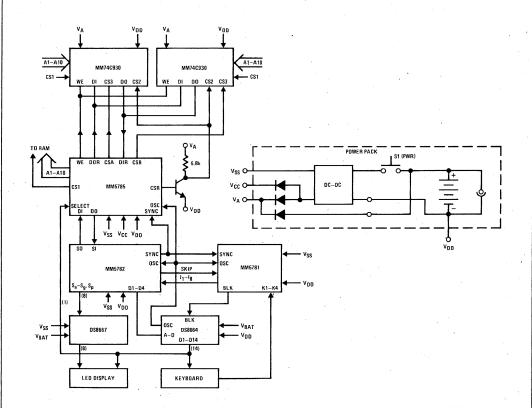

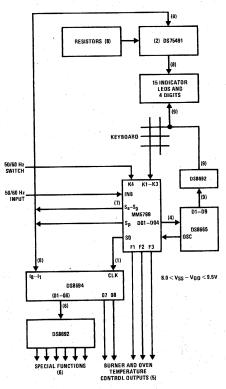

FIGURE 2. Hand-Held Calculator with Battery Augmented Memory (BAM)

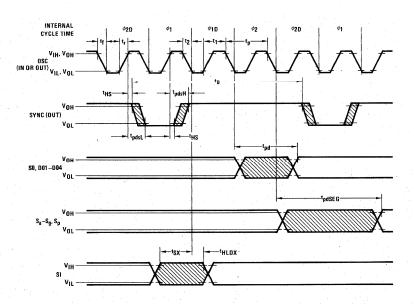

A power-on sequence is necessary to clear all registers and condition the MM5785 for data entry. Timing is described in *Figure 5*. Select must be toggled once before starting.

An interface circuit is required in a non-volatile battery back-up system using the MM74C930. An example is shown in Figure 6. Before the MM5785 is selected,  $P_{ON}$  is at a logical high level, Q1 is "OFF," and the

RAMs are disabled. If system power is removed, VSS collapses to Gnd, Q1 remains "OFF" so that false data cannot be entered during power up.

During normal operation,  $P_{ON}$  is in a logical low state and when the MM5785 is selected, Q1 turns "ON" to enable the RAMs. R<sub>L</sub> is chosen from the CSR I<sub>OH</sub> spec to insure saturation of Q1. CSR timing is shown in *Figure 5*.

(b) Read Mode (WE at Logical High Level. A0-A9, CSA-CSD and CS1 have Same Timing as Write Mode)

Note 1. Osc input duty cycle = -

Note 2. SYNC provides a 1 of 4 timing relationship with osc input, to establish osc edges as references for I/O timing.

FIGURE 3. Input/Output Waveform Timing

Start bit is always positive logic "1," logical high level The above pattern indicates a write condition with CSA selected.

FIGURE 4. Typical Bit Pattern

#### MM5788 printer interface chip

#### general description

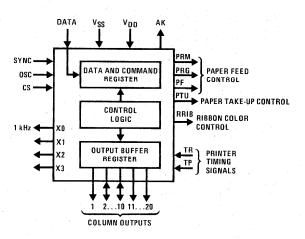

The MM5788 is an MOS/LSI device designed to interface the National Controller Oriented Processor sets with various rotating drum and start-stop printers, as shown in *Figure 1*. It will drive up to 20 parallel print columns, with controls for ribbon color, paper feed, and paper take-up. An additional 4-bit output port provides a 1 kHz tone signal and there are three general purpose outputs under control of the processor.

The MM5788 can also be used as a general purpose I/O chip. In this mode, ten column drivers are outputs and nine function as input/output ports, all under program control.

#### features

- Capable of driving Seiko Models 102, 104, 210, 220, 101T, 310 and 320 (20 columns)

- Paper feed inhibit for overprinting

- Multiple paper feeds (up to 15)

- Tone output for audio bleep under program control

- Internal power "ON" clear

- Single power supply operation

- TRI-STATE<sup>®</sup> handshake acknowledge to allow multiple MM5788's and other peripherals to be intermixed for system expansion

- General purpose I/O mode

- On-chip comparators to detect printer timing signals

#### block diagram

#### absolute maximum ratings

#### operating voltage range

Voltage at Any Pin Relative to Vss (All other pins connected to Vss) Ambient Operating Temperature  $\begin{array}{c} \text{Vss} + 0.3 \text{V to Vss} - 12.0 \text{V} \\ \text{Vss} + 0.3 \text{V to Vss} - 12.0 \text{V} \\ \text{O° C to } + 70 ^{\circ} \text{C} \\ \end{array}$ Ambient Storage Temperature Lead Temperature

-55°C to +150°C

$6.5 \le V_{SS} - V_{DD} \le 9.5 V$  (VSS is always the most positive supply voltage)

#### dc electrical characteristics (Ambient Operating Temperature)

|          | PARAMETER                                         | CONDITIONS                                                                             | MIN                  | TYP | MAX                  | UNITS |